# ЛОГИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

УДК 519.714.5

## Д.И. Черемисинов, Л.Д. Черемисинова

# СИНТЕЗ КОМБИНАЦИОННЫХ СХЕМ В БАЗИСЕ БИБЛИОТЕЧНЫХ ЭЛЕМЕНТОВ КМОП СБИС С УЧЕТОМ ЭНЕРГОПОТРЕБЛЕНИЯ

Рассматривается задача синтеза многоуровневых логических сетей в базисе библиотечных элементов КМОП СБИС, оптимизированных по критерию площади и среднему значению рассеиваемой мощности КМОП-микросхемы при ее реализации на кристалле СБИС. Предлагаемый подход основан на покрытии многоуровневой сети из вентилей и использовании специфики элементного базиса КМОП.

#### Введение

Задача синтеза состоит в представлении исходного функционального описания логической схемой из элементов технологической библиотеки изготовителя СБИС, каждый из которых характеризуется своей функцией и физическими характеристиками. Широко используемыми критериями оптимальности при синтезе являются площадь результирующего кристалла СБИС (функция от числа вентилей, транзисторов), быстродействие или (в последние годы) энергопотребление. В такой постановке задача синтеза является комбинаторно сложной. Она упрощается, если исходное функциональное описание представить сначала в виде многоуровневой схемы из простых элементов (вентилей И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ), а затем преобразовать ее в функционально эквивалентную схему из элементов целевой технологической библиотеки.

В большинстве систем проектирования процесс логического синтеза делится на две стадии: технологически независимую оптимизацию и технологическое отображение [1, 2]. Первая стадия синтеза ориентирована на оптимизацию и декомпозицию логики, а вторая — на перевод схемы из технологически независимого базиса в технологический. Цель первого этапа заключается в построении такого варианта представления схемы, который мог бы служить хорошей отправной точкой для этапа технологического отображения. При этом минимизируется сложность схемы из вентилей, измеряемая, как правило, числом вентилей, а в нашем случае и оценкой энергопотребления на логическом уровне. Цель второго этапа заключается в оптимальном переводе схемы в технологический базис.

В настоящей работе рассматривается задача энергосберегающего синтеза многоуровневых логических схем из библиотечных элементов, выполненных на основе технологии статических КМОП-схем, которая в настоящее время является доминирующей технологией в области цифровых СБИС. Проблема оценки энергопотребления статических КМОП-схем (по сравнению с динамическими) заключается в том, что компоненты СБИС, выполненные по этой технологии, потребляют подавляющую часть необходимой для их функционирования энергии во время их переключения [3-7]. Энергопотребление существенно зависит от переключательной активности элементов схемы, а она, в свою очередь, определяется последовательностью подаваемых входных воздействий на КМОП-схемы, т. е. динамикой функционирования. В работе предлагается метод технологического отображения, основанный на структурном покрытии многоуровневой логической сети из вентилей элементами КМОП-библиотеки. При покрытии минимизируются площадь и среднее значение мощности, рассеиваемой микросхемой КМОП СБИС. Рассматривается следующий случай: а) используется синхронная реализация схем; б) основные схемотехнические решения проектируемой схемы, такие как частота синхронизации и напряжение питания, фиксированы; в) для оценки энергопотребления в процессе синтеза и оптимизации логических схем используется статический метод (в противовес динамическому методу, в основе которого лежит моделирование), основанный на вероятностных характеристиках входных сигналов и функционально-структурных свойствах исследуемой схемы. Предполагается, что в качестве оценки энергопотребления

отображаемой в библиотечный базис многоуровневой схемы и ее фрагментов используется переключательная активность и что переключательные активности выходных полюсов всех ее вентилей и входных полюсов заданы.

#### 1. Синтез схем из библиотечных элементов

Энергопотребление схем на уровне логики в общем случае прямо пропорционально площади, занимаемой ею на кристалле СБИС. Это означает, что основной путь энергосбережения при функционировании логических схем прежде всего подразумевает сокращение площади, занимаемой схемой на кристалле СБИС. Практика показывает, что существующие методы, при которых оптимизируется сложность схемы, являются хорошей отправной точкой для развития методов минимизации энергопотребления логических схем. Применение этих методов в качестве канвы для разрабатываемых методов минимизации энергопотребления требует рассмотрения также новых критериев, используемых наряду с критериями минимизации площади схем. Эти критерии существенно зависят от технологии реализации синтезируемых логических схем.

#### 1.1. Элементный базис КМОП СБИС

Элементный базис содержит достаточно широкий спектр различных логических элементов, среди которых центральное место занимает комбинационная логика – простые древообразные схемы из вентилей И, ИЛИ, НЕ. В этот набор, как правило, входят элементы И, ИЛИ, И-НЕ, ИЛИ-НЕ на разное число входов (обычно на два – четыре, а иногда и шесть, восемь входов, как в базисе [8]) и древообразные схемы (из вентилей И, ИЛИ) с числом входных полюсов не более четырех и числом уровней два – четыре. За сложность (цену) библиотечного элемента можно принять число транзисторов его микросхемы (или число топологических базовых ячеек, размеры которых зависят от технологии изготовления КМОП-элементов). Это число прямо связано с площадью, занимаемой элементом на кристалле, и его емкостной нагрузкой, от которой существенно зависит энергопотребление элемента.

Элементный базис КМОП СБИС характеризуется наличием полного множества вентилей. Структуры элементов библиотеки можно представить древообразными сетями из вентилей И, ИЛИ, НЕ. Каждое из этих деревьев имеет ограниченное число листьевых вершин и ограниченный коэффициент ветвления выхода. КМОП-библиотека характеризуется тем, что для каждого элемента в ней, как правило, имеется элемент, реализующий двойственную функцию.

Так, в таблице приведены характеристики некоторых элементов КМОП-библиотеки, на примере которых будет демонстрироваться предлагаемый метод синтеза: n — число входных полюсов; k — суммарное число входных полюсов вентилей; l — число ярусов его древообразной структуры (кроме инвертора); t — число транзисторов его микросхемы. Элементы рассматриваемой КМОП-библиотеки имеют следующие ограничения:  $n \le 4$ ;  $k \le 9$ ;  $l \le 4$ ;  $t \le 12$ .

| Библиотечные<br>элементы                     | n       | k       | t       | l | Показатель логической эффективности | Схемы элементов                            |

|----------------------------------------------|---------|---------|---------|---|-------------------------------------|--------------------------------------------|

| HE                                           | 1       | 1       | 2       | 1 | 0,5                                 | A+ 1 → Y                                   |

| И-НЕ, ИЛИ-НЕ<br>NA, NA3, NA4<br>NO, NO3, NO4 | 2, 3, 4 | 2, 3, 4 | 4, 6, 8 | 2 | 0,5, 0,5, 0,5                       | A ← & A ← 1<br>B ← B ← C ← ← Y C ← ← Y C ← |

| И, ИЛИ<br>A, A3<br>O, O3                     | 2, 3    | 2, 3    | 6, 8    | 1 | 0,33; 0,37                          | A → & A → 1<br>B → Y B → C + → Y           |

Элементы КМОП-библиотеки

Окончание таблицы

| Библиотечные<br>элементы                       | n | k | l  | t | Показатель<br>логической<br>эффективности | Схемы элементов                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|---|---|----|---|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3И-2ИЛИ-НЕ<br>3ИЛИ-2И-НЕ<br>NOA3<br>NAO3       | 4 | 5 | 8  | 3 | 0,63                                      | A - 8   A -   8   B -   C -   D -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   O -   |

| 2-2И-2ИЛИ-НЕ<br>2-2ИЛИ-2И-НЕ<br>NOAA<br>NAOO   | 4 | 6 | 8  | 3 | 0,75                                      | A → &   A →   & B →   C → A → Y C →   D → Y D →   D → Y D →   D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → Y D → |

| 2И-3ИЛИ-НЕ<br>2ИЛИ-3И-НЕ<br>NO3A<br>NA3O       | 4 | 5 | 8  | 3 | 0,63                                      | Δ - &   Δ -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   & B -   |

| 2-2И-3ИЛИ-НЕ<br>2-2ИЛИ-3И-НЕ<br>NO3AA<br>NA3OO | 5 | 7 | 10 | 3 | 0,7                                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3И-3ИЛИ-НЕ<br>3ИЛИ-3И-НЕ<br>NO3A3<br>NA3O3     | 5 | 6 | 10 | 3 | 0,6                                       | A → & 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Для целей оценки эффективности вариантов отображения схем в технологический базис вводится количественный показатель его логической эффективности, выражающийся в числе полюсов покрываемой библиотечным элементом схемы, которое приходится на единицу его сложности — один транзистор. Логическая эффективность элемента равна отношению k/t числа входных полюсов вентилей, представляющих структуру этого библиотечного элемента, к числу транзисторов его микросхемы. Чем больше это отношение, тем выше функциональная эффективность элемента (для целей покрытия).

Из таблицы видно, что наиболее эффективными являются элементы с наиболее сложной структурой: NOAA (2-2И-2ИЛИ-НЕ) и NO3A3 (3И-3ИЛИ-НЕ) и двойственные им NAOO (2-2ИЛИ-2И-НЕ) и NA3O3 (3ИЛИ-3И-НЕ), наименее эффективными — инвертор и двухвходовые вентили И и ИЛИ (A2 и O2). Цена сложного элемента библиотеки, как правило, меньше суммы цен составляющих его вентилей, реализованных более простыми элементами. Например, элемент NOAA может быть реализован в виде композиции инвертора, двух элементов A2 и элемента O2. Цена элемента NOAA (восемь транзисторов) меньше цены композиции (2+8+4=14 транзисторов).

#### 1.2. Технологическое отображение

Последним и решающим этапом логического синтеза является техническое отображение, на этом этапе оптимизированная многоуровневая схема из вентилей технологически независимого базиса (называемая объектной) преобразуется в многоуровневую схему из библиотечных элементов путем локальных замен подсхем из вентилей. Основные подходы к решению задачи технологического отображения базируются на покрытии схемы из вентилей библиотечными элементами [1, 2, 9]. При покрытии делается попытка заменить группы связанных вентилей библиотечными элементами, минимизируя площадь результирующей схемы. При этом анализируются и оцениваются все или ограниченное множество возможных вариантов замен. В литературе предлагается множество методов покрытия, различающихся быстродействием и степенью приближения к оптимальному. Крайними (по быстродействию) являются методы чисто структурного и функционального покрытия [1].

При структурном покрытии задача технологического отображения сводится к оптимизации покрытия ориентированного ациклического графа, задающего исходную объектную схему, ациклическими подграфами, задающими структуры библиотечных элементов в том же вентильном базисе, что и покрываемая сеть. Функциональное покрытие основано на сравнении функций, реализуемых фрагментами покрываемой схемы и библиотечными элементами. Методы структурного покрытия имеют сравнительно небольшое время реализации, но качество решения сильно зависит от структуры покрываемой объектной схемы. Между тем методы функционального покрытия значительно проигрывают по быстродействию, даваемое ими решение в меньшей степени зависит от структуры объектной схемы. Методы структурного покрытия стали де-факто стандартом при проектировании СБИС с помощью САПР. Методы функционального покрытия лежат в основе средств ресинтеза, когда некоторая схема из библиотечных элементов оптимизируется путем локальных преобразований.

Основы методов структурного покрытия были заложены К. Койцером [10]. В его формулировке технологически независимая объектная сеть и каждый библиотечный элемент декомпозируются в сети из двухвходовых вентилей И-НЕ. Первая сеть представляется объектным графом – ориентированным ациклическим графом (ОАГ), вторая – модельным графом (тоже ОАГ). Проблема технологического отображения формулируется как задача покрытия объектного графа модельными. К. Койцер предложил алгоритм, основанный на методе динамического программирования и гарантирующий точное решение, если объектный и модельный графы являются деревьями. Метод синтеза, основанный на структурном покрытии, состоит из трех этапов: декомпозиции объектного ОАГ на непересекающиеся деревья, выполнения технологического отображения для каждого дерева, объединения результатов.

В основе предлагаемого ниже метода синтеза схем с пониженным энергопотреблением лежит структурное покрытие, так как эта процедура может быть сравнительно несложно адаптирована для целей минимизации энергопотребления. Методы структурного покрытия не предполагают кардинальную перестройку схемы, полученной на этапе технологически независимой оптимизации. Значит, качество искомого покрытия существенно зависит от структуры покрываемой многоуровневой схемы. Просчеты, допущенные при ее синтезе, не могут быть компенсированы в полной мере на этапе технологического отображения, поэтому в существующих САПР большое внимание уделяется этапу технологически независимой оптимизации и декомпозиции реализуемого описания в многоуровневую схему из вентилей.

#### 1.3. Выбор базовых вентилей технологически независимой схемы

Существуют разные подходы к выбору базовых вентилей при синтезе технологически независимой схемы. Обычно описание реализуемой логики транслируется (в результате минимизации) в эквивалентное И-ИЛИ-описание, которое на этапе декомпозиции переводится в однородный базис двухвходовых И-НЕ или ИЛИ-НЕ [1, 9]. Использование минимального числа базовых вентилей за счет их простоты (например, 2И-НЕ), как это принято в ряде известных САПР (например, MIS [11], SIS [12], ABC), приводит к повышению гранулярности логической сети, а значит, в общем случае может повысить и качество ее покрытия библиотечными элементами за счет увеличения числа вариантов покрытия. Однако в случае КМОП-базиса это преимущество может перекрываться значительно большим числом недостатков: усложняются представления библиотечных элементов (в таком «мелком» базисе); увеличивается число разных представлений одного и того же элемента; уменьшается быстродействие методов покрытия, что приводит, в свою очередь, к необходимости еще большего их огрубления.

Для случая КМОП-библиотеки значительно более привлекателен выбор технологически обусловленного базиса базовых вентилей [13]. В качестве базовых выбираются вентили, входящие в состав библиотечных элементов технологического базиса. Такой подход позволяет получать на этапе технологически независимой оптимизации логическую сеть, максимально приближенную к технологическому базису, а соответственно и применять более эффективные и простые алгоритмы покрытия при технологическом отображении. Кроме того, такой подход позволяет упростить сами модельные представления библиотечных элементов (они представляются в том же вентильном базисе, что и покрываемая объектная сеть) и их число (а значит, и размер библиотеки), что немаловажно для увеличения быстродействия алгоритма покрытия.

Если проанализировать состав КМОП-библиотеки, то можно заметить, что структуры всех сложных элементов могут быть представлены схемами из чередующихся вентилей И и ИЛИ. Это значит, что простое представление многоместных функций И или ИЛИ в виде композиции двухместных не даст новых возможностей для покрытия, но приведет к упомянутым негативным последствиям. Поэтому для рассматриваемого технологического базиса целесообразно выбрать в качестве базовых вентили НЕ, И и ИЛИ с ограниченным числом входов, не большим максимального числа входов вентилей (И-НЕ, ИЛИ-НЕ) этой библиотеки.

### 2. Оценка энергопотребления в процессе синтеза

В общем случае мощность рассеивания энергии логической схемой является сложной функцией, зависящей от задержек распространения сигналов через схему, частоты синхронизации, технологических параметров изготовления, топологии микросхемы, а в случае КМОП-технологии существенно зависящей от последовательности прилагаемых к схеме входных воздействий. В типичных КМОП-цепях около 80 % всей рассеиваемой энергии приходится на ее динамическую составляющую [5], порождаемую нестационарным поведением узлов схемы. Согласно упрощенной модели энергия рассеивается КМОП-микросхемой всякий раз, когда изменяется сигнал на ее выходе. Средняя величина мощности, рассеиваемой на выходе синхронной микросхемы, выражается известным соотношением [3–5]

$$P_{dyn} = \frac{1}{2} V_{dd}^2 f_{clk} E_s C_L, \tag{1}$$

где  $V_{dd}$  — напряжение питания;  $f_{clk}$  — частота синхронизации;  $E_s$  — переключательная активность выхода схемы, определяемая как математическое ожидание числа логических переходов сигнала (из 1 в 0 или из 0 в 1) за один период синхронизации;  $C_L$  — емкостная нагрузка микросхемы.

Из формулы (1) следует, что на логическом уровне, когда схема только синтезируется, энергопотребление схемы может быть снижено путем такого ее преобразования, которое обеспечивает уменьшение сложности (числа транзисторов) и переключательной активности логической схемы без изменения ее функциональности. На уровне функционального описания схемы оценка энергопотребления на основе изменения переключательной активности предсказывает эффект изменения энергопотребления в результате оптимизации, а не его абсолютную величину. Такая оценка может обеспечить уменьшение энергопотребления будущей схемы еще на этапе функциональных преобразований.

В основе метода оценки переключательной активности лежит подход, основанный на задании вероятностей переключения входных сигналов, которые отражают частоту смены их значений и используются для вычисления вероятностей переключения сигналов на выходах узлов схемы. Для оценки вариантов оптимизации схемы на логическом уровне достаточно использовать простые оценки изменения переключательной активности при выборе вариантов оптимизации. Эти оценки выведены в предположении временной и пространственной независимости сигналов на входах элементов схемы [6, 7]. Переключательная активность полюса  $z_i$  схемы вычисляется как

$$E(z_i) = 2 p_i (1 - p_i), (2)$$

где  $p_i$  — сигнальная вероятность полюса  $z_i$ , определяемая средней долей тактов, на которых сигнал на полюсе  $z_i$  имеет значение 1. Сигнальные вероятности выходных полюсов простых элементов типа инвертора, И, ИЛИ с n(e) входными полюсами могут быть подсчитаны, если известны сигнальные вероятности  $p_i$  для входных полюсов [4, 5]:

$$p_e^{\neg} = 1 - p_1; \ p_e^{\wedge} = \prod_{i=1}^{n(e)} p_i; p_e^{\vee} = 1 - \prod_{i=1}^{n(e)} (1 - p_i).$$

(3)

Далее считается, что перед выполнением покрытия для всех полюсов покрываемой схемы из вентилей подсчитаны переключательные активности.

#### 3. Основные определения

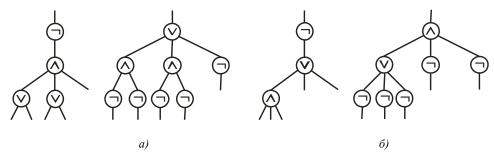

В процессе покрытия структурные схемы библиотечных элементов сравниваются с фрагментами покрываемой схемы и в случае полного совпадения заменяют их. Соответственно каждый библиотечный элемент должен быть представлен разными структурами, реализующими его функцию. Как уже было отмечено, основная масса наиболее эффективных элементов реализует инверсную логику, а отдельно выполненные инверторы являются достаточно дорогими КМОП-элементами. В связи с этим при структурном покрытии схемы наряду со структурами элементов, отображающими реализуемую ими функцию, в библиотеку структурных описаний предлагается включать также двойственные структуры, получаемые путем переноса инверторов с выходов на входы (смены вентилей И на ИЛИ, а ИЛИ на И) (рис. 1). Например, элемент 2И-2ИЛИ-НЕ (NOA), реализующий функцию  $\overline{ab \lor c}$ , порождает элемент 2ИЛИ-2И (AON) с инверторами на входах, реализующий функцию ( $\overline{a} \lor \overline{b}$ )  $\overline{c}$ .

Рис. 1. Структуры двух нетривиальных элементов КМОП-библиотеки: a) 2-2ИЛИ-3И-НЕ (NA3OO);  $\delta$ ) 3И-3ИЛИ-НЕ (NO3A3)

### 3.1. Графовое представление покрываемой схемы

Покрываемая многовыходная логическая сеть представляется множеством связанных между собой базовых вентилей. Каждый вентиль реализует некоторую логическую функцию, обозначим множество этих функций через  $\Phi = \{ \phi_1, \phi_2, ..., \phi_l \}$ . Будем представлять исходную логическую сеть ориентированным ациклическим графом G = (V, U), называемым далее объектным. Вершины графа  $v_i \in V$  соответствуют базовым вентилям и входным полюсам схемы. Вершины  $v_i$  и  $v_j$  связываются дугой  $(v_i, v_j) \in U$ , направленной из  $v_i$  в  $v_j$ , если выход вентиля или входной полюс, приписанный вершине  $v_i$ , связан с одним из входов элемента, приписанного вершине  $v_j$ . Таким образом, граф, представляющий логическую сеть, имеющую n входных и m выходных полюсов, имеет ровно m вершин  $v_k$  с полустепенью исхода  $d^{-1}(v_k) = 0$  и n вершин с полустепенью захода  $d^{+1}(v_k) = 0$ . Каждая вершина  $v_k$  с  $d^{+1}(v_k) \neq 0$  помечается функцией  $\phi(v_k) \in \Phi$ , реализуемой соответствующим базовым вентилем.

#### 3.2. Графовое представление библиотечных элементов

Структурное описание библиотечного элемента представляет собой одновыходную многоуровневую логическую сеть из базовых вентилей. В ней выход каждого вентиля нагружен на не более чем один элемент. Множество различных функций базовых вентилей сети i-го библиотечного элемента обозначим через  $\Phi_i \subseteq \Phi$ . В случае КМОП-библиотеки (см. таблицу)  $\Phi = \{\text{HE, И2, И3, И4, ИЛИ2, ИЛИ3, ИЛИ4}\}.$

Каждый библиотечный элемент представляется ориентированным графом  $H_i = (W_i, E_i)$ , называемым далее модельным. Это представление в общем случае не единственно, соответственно получается более чем один модельный граф. Граф, описывающий структуру любого библиотечного элемента, есть дерево. В нем существуют вершина, которую можно принять за корень (вершина с нулевой полустепенью исхода), и листья (вершины с нулевыми полустепенями захода). Вершины  $w_{ki}$  графов  $H_i$  со степенями захода  $d^{+1}(w_{ki}) > 0$  (внутренние вершины) помечаются функциями  $\phi(w_{ki}) \in \Phi$ , реализуемыми базовыми вентилями. За стоимость и логическую эффективность модельного графа примем число транзисторов и логическую эффективность соответствующего библиотечного элемента.

## 3.3. Операции на графах

Подграфом  $G_k$  объектного графа G = (V, U) является граф  $G_k = (V_k, U_k)$ , где  $V_k \subseteq V$ , а  $U_k = \{u_i = (v_{ir}, v_{is})/\ u_i \in U, \ v_{ir}, \ v_{is} \in V_k\}$ . Множеством достижимости вершины  $v_k \in V$  называется множество  $P(v_k)$  вершин-предшественников  $v_k$ :  $P(v_k) = \{v_i/(v_i,v_k) \in U\}$ . Разностью графов G = (V, U) и  $G_k = (V_k, U_k)$  называется граф G' = (V', U'), в котором  $U' = U \setminus U_k$ , а множество V' содержит вершины из V, степени которых после исключения дуг из множества U отличны от V.

Ориентированный граф  $G_k = (V_k, U_k)$  покрывается графом  $H_l = (W_l, E_l)$ , если существует отображение  $\psi: V_k \to W_l$ , такое, что выполняются следующие условия:

- 1) если вершинам  $v_i \in V_k$  и  $\psi(v_i) \in W_l$  приписаны функции (т. е. если мощности множеств вершин-предшественников  $|P(v_i)|$  и  $|P(\psi(v_i))| > 0$ ), то  $\phi(v_i) = \phi(\psi(v_i))$ ;

- 2) любая дуга  $u_j \in U_k$ , направленная из  $v_{jr}$  в  $v_{js}$ , отображается в дугу  $e_i \in E_l$ , направленную из  $\psi(v_{ir})$  в  $\psi(v_{is})$ .

В свою очередь, граф  $H_l$  полностью отображается на  $G_k$ , если существует обратное отображение  $\psi^{-1}$ :  $W_l \to V_k$ , что сводится к выполнению условия 2 и для дуг графа  $H_l$ . В этом случае графы изоморфны и их разность  $H_l \setminus G_k = \emptyset$ . Множество  $\{G_1, G_2, ..., G_k\}$  подграфов представляет покрытие графа G, если  $U_1 \cup U_2 \cup ... \cup U_k = U$ ,  $V_1 \cup V_2 \cup ... \cup V_k = V$  (при этом может иметь место  $V_i \cap V_i \neq \emptyset$ ,  $i \neq j$ ).

## 3.4. Задание объектного и модельного графов

Определим для вершин графов (объектного G = (V, U) и модельных  $H_i = (W_i, E_i)$ ) полуокрестности захода и исхода. Для каждой вершины  $v_i \in V$  ( $w_i \in W_l$ ) указываются множества  $P(v_i)$  и  $S(v_i)$  ( $P(w_i)$  и  $S(w_i)$ ) вершин, из которых она непосредственно достижима и которые непосредственно достижимы из нее. Мощности этих множеств для вершины  $v_i$  равны соответственно ее полустепеням захода  $d^{-1}(v_i)$  и исхода  $d^{-1}(v_i)$ .

Будем называть кластером графа  $G_k = (V,U)$ , порождаемым вершиной  $v_k \in V$ , дерево  $G_k = (V_k, U_k)$  на G, определяемое рекурсивно:  $v_k \in V_k$ , и любая  $v_i \in V$  также включается в  $V_k$ , если  $v_i \in P(v_j \in V_k)$ , при этом в  $V_k$  включается  $d^{-1}(v_i)$  копий вершины  $v_i \in V_k$ . Множество ребер кластера определяется следующим образом:  $U_k = \{u_i = (v_{ir}, v_{is}) | u_i \in U, v_{ir}, v_{is} \in V_k\}$ . Из способа построения подграфа  $G_k$  вытекает утверждение, что кластер  $G_k = (V_k, U_k)$  графа  $G_k$  порождаемый вершиной  $v_k \in V$ , представляет собой дерево.

Для любой вершины кластера  $v_i \in V_k$  число достижимых из нее вершин ( $|S(v_i)|$ ) равно 1. Будем обозначать эту единственную вершину через  $s(v_i)$ . Это свойство имеет место и для вершин модельных графов, так как они являются деревьями.

Разобьем вершины кластера  $G_k$  по ярусам: к первому ярусу отнесем порождающую вершину  $v_k$ , обозначив ее как  $v_{k1}^{-1}$ . Ко второму ярусу отнесем вершины  $v_{kj}^2 \in P(v_{k1}^1)$  и соответственно к p-му ярусу — вершины  $v_{kj}^p \in \bigcup_i P(v_k^{p-1}_i)$ . Аналогично кластеру разобьем вершины любого

модельного графа  $H_l$  по ярусам:  $w_{l1}^{-1}$ ;  $w_{lj}^{-2} \in P(w_{l1}^{-1})$ ; ...;  $w_{lj}^{-p} \in \bigcup_i P(w_{li}^{-p-1})$ . Модельный граф, выбираемый для анализа на покрытие кластера, будем называть образцом.

## 4. Структурное покрытие логической сети

Задача покрытия объектного графа G модельными графами  $H_i$  заключается в разбиении графа G на подграфы  $G_k = (V_k, U_k)$ , каждый из которых покрывается некоторым образцом  $H_i$ . Основными операциями покрытия являются: выделение кластера, сравнение с образцом, выбор образца. Метод покрытия основан на последовательном выделении кластеров  $G_k$  графа G, сравнении каждого из них на предмет покрытия его части образцами  $H_l$  и замене его части  $G_k$  графом  $H_l$ , дающим наибольшее значение выбранных критериев оптимизации. Таким образом, метод обеспечивает локальную оптимизацию и является приближенным.

В процессе покрытия граф G сжимается за счет исключения из него покрытых подграфов. Одновременно наращивается (начиная с пустого) результирующий граф E, представляющий

логическую сеть из библиотечных элементов, эквивалентную исходной. Сжатие графа G осуществляется заменой его разностью графов  $G \setminus G_k$ '.

## 4.1. Критерий оптимизации покрытия

Необходимо получить такой вариант покрытия схемы, который обеспечивал бы минимум площади и энергопотребления. В предлагаемом методе в качестве первого критерия оптимизации принимается площадь полученной в результате покрытия схемы, которая измеряется суммарным числом транзисторов всех библиотечных элементов и оценивается суммой стоимостей модельных графов, входящих в покрытие объектного графа. Соответственно при поиске образца  $H_l = (W_l, E_l)$  для покрытия части кластера  $G_k = (V_k, U_k)$  за критерий  $k^1$  эффективности его применения принимается относительная стоимость покрытия одной вершины кластера, измеряемая отношением числа покрытых вершин к стоимости соответствующего модельного графа. Чем больше это число, тем более желателен вариант покрытия.

В том случае, когда граф  $H_l$  полностью отображается на  $G_k$  (т. е. существует отображение  $\psi^{-1}$ :  $W_l \to V_k$ ) и все внутренние вершины покрытого подграфа кластера  $G_k$  имеют в графе G степень исхода, равную 1, значение  $k^1$  равно значению логической эффективности графа  $H_l$ . Для КМОП-базиса нет смысла рассматривать вариант покрытия фрагмента кластера модельным графом, при котором  $H_l \setminus G_k \neq \emptyset$  (не все вершины графа  $H_l$  участвуют в покрытии), так как они всегда проиграют любому варианту с  $H_m \setminus G_k = \emptyset$  (все вершины графа  $H_m$  участвуют в покрытии).

Энергопотребление схемы, полученной в результате покрытия, можно оценить суммой переключательных активностей всех полюсов схемы. Так как энергопотребление существенно зависит от сложности схемы, то ее переключательная активность является только одним из факторов, влияющих на величину энергопотребления схемы; соответственно она может быть принята только в качестве второго критерия  $k^2$  эффективности образца для покрытия.

Если пренебречь задержкой сигналов в логических элементах, то при оценке энергопотребления можно пренебречь также и интенсивностью переключений сигналов на внутренних полюсах библиотечных элементов. Это допущение обосновывается тем, что наиболее существенный вклад в паразитную емкость схемы вносят соединительные линии, и на перезарядку этой емкости в процессе переключений сигналов тратится основная доля расходуемой мощности источника питания. Отсюда схему, реализуемую по КМОП-технологии, нужно покрывать библиотечными элементами так, чтобы как можно больше узлов схемы с наибольшей переключательной активностью оказалось внутри библиотечных элементов [6, 7]. Следовательно, за значение критерия  $k^2$  принимается сумма переключательных активностей элементов, которые соответствуют покрытым вершинам, ставшим внутренними вершинами покрывающего образца.

#### 4.2. Поиск варианта покрытия

Порядок выбора порождающих (корневых) вершин кластера определяется очередью Q. Первоначально в эту очередь вносятся вершины объектного графа, соответствующие выходам исходной сети (они могут иметь и ненулевые степени исхода). Далее в эту очередь после выбора очередного варианта покрытия вносятся те помеченные вершины объектного графа, которые являются предшественниками покрытых вершин. Процесс выделения кластеров и покрытия заканчивается, когда  $Q = \emptyset$  и граф  $G = \emptyset$ .

Кластеры  $G_k$  графа G в явном виде не выделяются. Выбирается корневая вершина  $v_k \in Q$ , определяющая кластер  $G_k$ , и перебираются модельные графы. Для пары  $v_k$ ,  $H_l$  выделяется подграф  $G^p_k$  кластера, который в качестве корневой имеет вершину  $v_k$  и покрывается подграфом  $H_l$ . Подсчитываются критерии эффективности  $k^1$  и  $k^2$ .

Выбор образца осуществляется путем просмотра образцов библиотеки, сравнения их с кластером и при положительном ответе — путем подсчета оценок покрытия. После окончания этого процесса для покрытия выбирается один лучший образец.

Сравнение кластера  $G_k = (V_k, U_k)$ , порождаемого корневой вершиной  $v_k$ , с модельным графом  $H_l = (W_l, E_l)$  сводится к размещению последнего на кластере. Это размещение производится путем последовательного наложения на  $G_k$  ветвей графа  $H_l$ . После размещения первой ветви делается попытка «размещения» второй ветви на части графа  $G_k$ , не покрытой первой ветвью

части графа  $G_k$ , и т. д. (аналогично тому, как это делается при обходе дерева поиска [14]). Размещение ветви производится путем перебора вариантов установления соответствия между очередной вершиной  $w_{li}^{\ j}$  ветви графа  $H_l$  и одной из вершин  $v_{kp}^{\ j}$  j-го яруса последователей покрытой вершины (j-1)-го яруса графа  $G_k$ . Если для вершин выполняются условия наложения

$$|P(w^j{}_{li})| = |P(v^j{}_{kp})|$$

и если  $\phi(u^j{}_{li})$  и  $\phi(v^j{}_{kp})$  помечены, то одинаково,

делается прямой ход — переход к следующему ярусу. После размещения последней вершины графа  $H_l$  подсчитываются соответствующие значения критериев и сравниваются с наилучшими из ранее полученных. Если  $k^1$  или  $k^2$  (при равенстве  $k^1$ ) больше значений для лучшего из ранее полученных вариантов покрытия, текущий вариант покрытия запоминается. Если же при сравнении  $v_{kp}^{\ \ j}$  и  $w^j_{li}$  хотя бы одно из условий (4) не выполняется, то делается обратный ход, который состоит в выборе очередной из непроверенных вершин  $v_{kp}^{\ \ j}$  j-го яруса, если они имеются. Иначе производится переход на ярус j-1, если j>1; в противном случае перебор вариантов покрытия  $G_k=(V_k,U_k)$  графом  $H_l=(W_l,E_l)$  заканчивается.

# 4.3. Повышение быстродействия алгоритма покрытия

Основной перебор при выполнении покрытия сосредоточен в процедуре размещения образца на кластере. Этот перебор выполняется для каждого образца библиотеки. Следующие процедуры сокращают этот перебор.

- 1. Поиск и покрытие подграфов объектного графа, допускающих покрытие единственным образом (единственным модельным графом). В простейшем случае такими подграфами являются вершины с большими степенями захода, для которых существует единственный вариант покрытия (например, для базисного набора серии К1574 [8] это число больше трех).

- 2. Упорядочение образцов. Если упорядочить модельные графы  $H_j$  по убыванию их эффективности (шестой столбец таблицы), то, сравнивая их по порядку с выделяемым на некотором шаге алгоритма покрытия кластером  $G_k$ , можно сократить в ряде случаев перебор. Так, если для некоторого  $H_l$  значение  $H_l \setminus G_k = \emptyset$ , то можно не производить сравнение кластера  $G_k$  с другими графами  $H_i$ , поскольку они имеют меньшую эффективность и покрывают, следовательно, меньшую часть графа G. Можно ограничиться лишь поиском варианта покрытия этим графом с наибольшим значением критерия  $k^2$ .

- 3. Топологическая сортировка объектного и модельных графов. Сортировка модельного графа  $H_l$  (он есть дерево) заключается в упорядочении ветвей дерева слева направо по убыванию их сложности. Ветвь P помещается левее ветви R, если P длиннее ветви R или (если они равны по длине) при просмотре вершин от корня в ветви P раньше встретится вершина с большей полустепенью захода, чем в ветви R. Сортировка позволит быстрее давать ответ на вопрос, можно ли покрыть фрагмент кластера заданным образцом. Аналогичная процедура выполняется и для объектного графа.

### 4.4. Пример

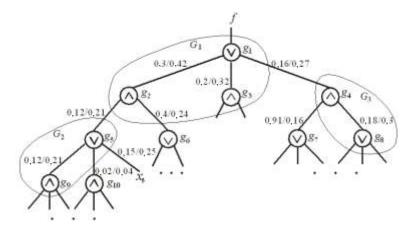

Покроем фрагмент объектной схемы в базисе вентилей И, ИЛИ, НЕ (рис. 2) элементами КМОП-библиотеки, заданной в таблице. На рис. 2 для выходного узла каждого вентиля указаны (через слэш) сигнальная вероятность и переключательная активность соответствующего сигнала, вычисленные согласно формулам (2) и (3). Модельные графы для некоторых библиотечных элементов (с наибольшей логической эффективностью) приведены на рис. 1. На рис. 2 показаны подграфы  $G_i$  (входящие в них вентили обведены тонкой сплошной линией) объектного графа, покрываемые выбранными модельными графами. При выборе для покрытия фрагмента кластера с порождающей вершиной f возможны два конкурирующих (по критерию стоимости  $k^1$ ) варианта покрытия модельным графом, соответствующим библиотечному элементу 2-2ИЛИ-3И-НЕ (NA3OO) (логическая эффективность равна 0,7):  $\{v_1, v_2, v_3\}$ ,  $\{v_1, v_2, v_4\}$  и  $\{v_1, v_3, v_4\}$ . Первый вариант  $\{v_1, v_2, v_3\}$  более предпочтителен по критерию энергопотребления  $k^2$ : сумма переключательных активностей внутренних элементов фрагмента равна 0,74. Анало-

гично при выборе для покрытия фрагмента кластера с порождающей вершиной  $g_4$  возможны также два конкурирующих варианта.

Рис. 2. Результат покрытия фрагмента объектной сети модельными графами

Ниже приведены пары «подграф  $G_i$  – библиотечный элемент, соответствующий модельному графу, покрывающему граф  $G_i$ »:

```

G_1 — 2-2ИЛИ-3И-НЕ (NA3OO);

G_2 — 3И-3ИЛИ-НЕ (NO3A3);

G_3 — 3ИЛИ-2И-НЕ (NAO3).

```

При покрытии графа  $G_1$  вентильной схемы использовалось двойственное представление элемента 2-2ИЛИ-3И-НЕ в вентильном базисе, в результате чего на входах элемента 2-2ИЛИ-3И-НЕ появились инверторы.

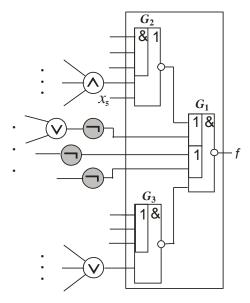

Рис. 3. Фрагмент схемы в базисе элементов КМОП-библиотеки

На рис. 3 приведен фрагмент схемы из элементов КМОП-библиотеки, соответствующий результату покрытия фрагмента схемы из вентилей (см. рис. 2). Вершины объектного графа, которым приписаны инверторы, введенные в процессе покрытия, затемнены.

#### Заключение

Предложен метод синтеза многоуровневых логических сетей в базисе библиотечных элементов КМОП СБИС. Метод основан на покрытии многоуровневых схем из вентилей И, ИЛИ (и инверторов) с ограниченным числом входных полюсов подсхемами, представленными в том же вентильном базисе и реализующими элементы КМОП-библиотеки. За критерии оптимизации приняты площадь и среднее значение рассеиваемой мощности КМОП-микросхемы. Метод реализован в рамках программного комплекса автоматизации проектирования интегральных микросхем с пониженным энергопотреблением, выполняемых по КМОП-технологии [15]. В рамках этой системы выполнению этапа синтеза многоуровневых логических сетей в базисе библиотечных элементов КМОП СБИС предшествует этап построения схемы в технологически обусловленном базисе вентилей НЕ, И и ИЛИ с ограниченным числом входов [16]. Синтез схемы из вентилей, которая является основой для покрытия элементами КМОП-библиотеки с помощью предлагаемого выше метода, производится с учетом площади и переключательной активности КМОП-микросхемы при ее реализации на кристалле СБИС.

### Список литературы

- 1. Брейтон, Р.К. Синтез многоуровневых комбинационных логических схем / Р.К. Брейтон, Г.Д. Хэчтел, А.Л. Санджованни-Винчентелли // ТИИЭР. 1990. Т. 78, № 2. С. 38-83.

- 2. BooleDozer : Logic synthesis for ASICs / L. Stok [et al.] // IBM J. Res. and Dev. 1996. Vol. 40, N<sub>2</sub> 4. P. 407–430.

- 3. Рабаи, Ж.М. Цифровые интегральные схемы. Методология проектирования / Ж.М. Рабаи, А. Чандракасан, Б. Николич. М. : Вильямс, 2007. 912 с.

- 4. Уэйкерли, Дж. Проектирование цифровых устройств. Т. 1 / Дж. Уэйкерли. М. : Постмаркет, 2002.-544 с.

- 5. Benini, L. Logic Synthesis for Low Power / L. Benini, G. De Micheli; eds. S. Hassoun, T. Sasao, R.K. Brayton // Logic Synthesis and Verification. Boston, Dardrecht, London: Kluwer Academic Publishers, 2002. P. 197–224.

- 6. Pedram, M. Power Minimization in IC Design: Principles and Applications / M. Pedram // ACM Transactions Design Automation Electronic Systems. 1996. Vol. 1. P. 3–56.

- 7. Roy, K. Low Power CMOS VLSI Circuit Design / K. Roy, S.C. Prasad. N. Y. : John Wiley and Sons Inc., 2000.-376~p.

- 8. Лукошко, Г. КМОП базовые матричные кристаллы серии К1574 / Г. Лукошко, Е. Коннов // Радиолюбитель. 1997. № 9. С. 39—40.

- 9. Stok, L. Technology mapping / L. Stok, Tiwari V. // Logic Synthesis and Verification / Eds. S. Hassoun, T. Sasao, R.K. Brayton. Boston, Dardrecht, London: Kluwer Academic Publishers, 2002. P. 115–140.

- 10. Keutzer, K. DAGON: Technology binding and local optimization by DAG matching / K. Keutzer // Proc. 24th ACM/IEEE Design Automation Conf. N. Y., USA, 1987. P. 617–623.

- 11. Technology mapping in MIS / E. Detjens [et al.] // Proc. IEEE Int. Conf. on CAD (ICCAD). Santa Clara, CA, USA, 1987. P. 116–119.

- 12. SIS: A System for Sequential Circuit Synthesis / E.M. Sentovich [et al.] // University of California, Berkeley, Technical Report No. UCB/ERL M92/41 [Electronic resource]. 1992 Mode of access: http://www.eecs.berkeley.edu/Pubs/TechRpts/1992/ERL-92-41.pdf. Date of access: 12.06.2013

- 13. Черемисинова, Л.Д. Синтез и оптимизация комбинационных структур СБИС / Л.Д. Черемисинова. Минск : ОИПИ НАН Беларуси, 2005. 236 с.

- 14. Закревский, А.Д. Логические основы проектирования дискретных устройств / А.Д. Закревский, Ю.В. Поттосин, Л.Д. Черемисинова. М.: Физматлит, 2007. 589 с.

- 15. Синтез логических КМОП-схем с пониженным энергопотреблением / П.Н. Бибило [и др.] // Проблемы разработки перспективных микро- и наноэлектронных систем : сб. тр. / под ред. А.Л. Стемпковского. М. : ИППМ РАН, 2012. С. 73–78.

16. Черемисинова, Л.Д. Синтез многоуровневых логических схем с учетом энергопотребления / Л.Д. Черемисинова, Н.А. Кириенко // Информационные технологии. — 2013. — № 3. — С. 8—14.

Поступила 29.05.2013

Объединенный институт проблем информатики НАН Беларуси, Минск, Сурганова, 6 e-mail: cdl@newman.bas-net.by, cher@newman.bas-net.by

# D.I. Cheremisinov, L.D. Cheremisinova

# POWER DRIVEN SYNTHESIS OF COMBINATIONAL CIRCUITS ON THE BASE OF CMOS VLSI LIBRARY ELEMENTS

A problem of synthesis of multi-level logical networks using CMOS VLSI cell library is considered. The networks are optimized with respect to the die size and average dissipated power by CMOS-circuit implemented on a VLSI chip. The suggested approach is based on covering multilevel gate network and on taking into account specific features of the CMOS cell basis.